Publication

- First Demonstration of Ultra-low Dit Top-Gated Ferroelectric Oxide-Semiconductor Memtransistor with Record Performance by Channel Defect Self-Compensation Effect for BEOL-Compatible Non-Volatile Logic Switch

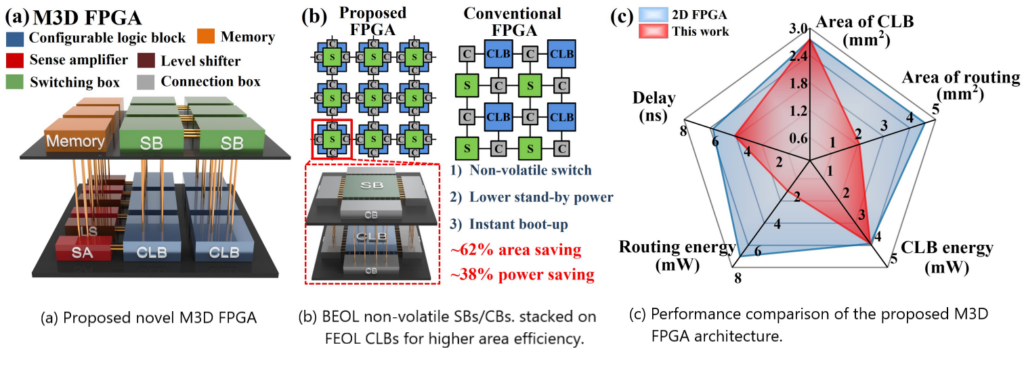

We demonstrate, for the first time, a short-channel (L G :40nm) back-end-of-line (BEOL) compatible top-gated (TG) self-aligned FeFETs with the ultra-low interface/bulk trap density (D it /D bulk ) down to 10 11 cm -2 eV -1 , a 100x improvement over conventional amorphous Indium-Gallium-Zinc-Oxide (IGZO) devices. High memory and drive performance are both achieved, exhibiting a large and stable memory window of 2.1V, excellent endurance exceeding 10 7 cycles, close-to-ideal subthreshold swing (S.S.) of 62mV/dec., and the record-low read-after-write delay of 200ns. This is accomplished by utilizing the defect self-compensation effect in the ITO-IGZO heterojunction channels for ferroelectric top-gate stack stabilization. We leverage these advantages and proposed a novel Monolithic 3D (M3D) FPGA architecture with the demonstrated short-channel (L G :40nm) BEOL dual-gated (DG) merged memory-logic FeFETs with excellent drive performance as a non-volatile reconfigurable interconnect switch. Our BEOL-compatible DG FeFET switch enables a compact interconnect switch fabrics with a V/2 bias scheme, featuring excellent G on /G off of 10 6 , ultra-low sub-pA leakage, disturb-free, and sneak-current-free read-write operation. This work sets new oxide-semiconductor FeFET performance records useful for future BEOL nonvolatile logic applications.

Researcher/Author from Department of Electrical and Computer Engineering:

Aaron Voon-Yew Thean; Evgeny Zamburg; Chun-Kuei Chen; Zihang Fang; Sonu Hooda; Manohar Lal; Umesh Chand; Zefeng Xu; Jieming Pan; Shih-Hao Tsai

Published in: 2022 International Electron Devices Meeting (IEDM)

- Home

- First Demonstration of Ultra-low Dit Top-Gated Ferroelectric Oxide-Semiconductor Memtransistor with Record Performance by Channel Defect Self-Compensation Effect for BEOL-Compatible Non-Volatile Logic Switch

Singapore Hybrid-Integrated Next-Generation μ-Electronics (SHINE) Centre

- Block E6, #E6-5-3, 5 Engineering Drive 1, Singapore 117608

- +65 6601 8522

- shine@nus.edu.sg