Publication

- High-Performance Top-Gated and Double-Gated Oxide–Semiconductor Ferroelectric Field-Effect Transistor Enabled by Channel Defect Self-Compensation Effect

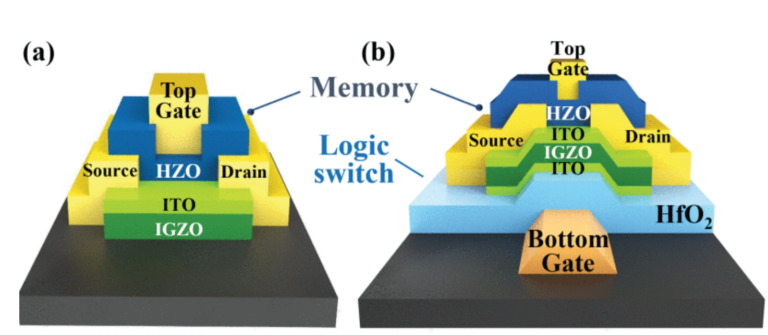

In this article, we demonstrate a low-thermal budget defect-engineered process to achieve top-gated (TG) oxide–semiconductor ferroelectric field-effect transistors (FeFETs). The demonstrated TG FeFETs, with the channel length scaled down to 40 nm, exhibit a highly stabilized ferroelectric memory window (MW) of 2 V and a high current ON/OFF ratio of 106. This is achieved by an engineered InGaZnOx (IGZO) and InSnOx (ITO) heterojunction channel that produces the defect self-compensation effect to passivate the intrinsic oxygen-deficient defects, existing in the indium-gallium-zinc-oxide (IGZO) channel interface and bulk. Effective interface/bulk defects passivation with good control of defect-induced channel carrier concentration has been notoriously difficult to achieve. Hence, realizing performant TG oxide-based FeFETs with back-end-of-line (BEOL) thermal budget constraints remains a fundamental challenge. Our study shows that heterojunction channel engineering on FETs and FeFETs can be a reliable solution to overcome this challenge. With such a technique, we can now enable double-gated (DG) ITO–IGZO FeFET and FETs. Such devices can enable BEOL-compatible reconfigurable nonvolatile logic switches that provide extremely low off-state leakage, high switch conductance ratio, and memory read-write disturb-free features.

Researcher/Author:

Aaron Voon-Yew Thean, Chun-Kuei Chen, Sonu Hooda, Zihang Fang, Manohar Lal, Zefeng Xu, Jieming Pan, Shih-Hao Tsai, and Evgeny Zamburg

Published in: IEEE Transactions on Electron Devices ( Volume: 70, Issue: 4, April 2023) International Electron Devices Meeting (IEDM)

Page(s): 2098 – 2105

- Home

- High-Performance Top-Gated and Double-Gated Oxide–Semiconductor Ferroelectric Field-Effect Transistor Enabled by Channel Defect Self-Compensation Effect

Singapore Hybrid-Integrated Next-Generation μ-Electronics (SHINE) Centre

- Block E6, #E6-5-3, 5 Engineering Drive 1, Singapore 117608

- +65 6601 8522

- shine@nus.edu.sg