Publication

- Negative-U Defect Passivation in Oxide-Semiconductor by Channel Defect Self-Compensation Effect to achieve Low Bias Stress VTH Instability of Low-Thermal Budget IGZO TFT and FeFETs

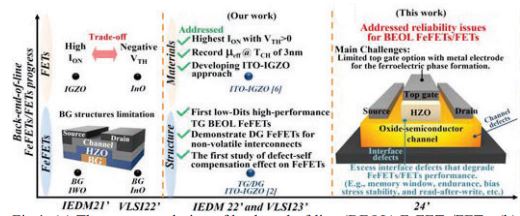

In this work, we elucidate the fundamental bias stress reliability mechanism in oxide-semiconductor devices and provided guidelines to improve interface/bulk-induced V TH degradation. We provide further insights into the defect-self compensation effect for the bilayer ITO-IGZO channel. Specifically, how our process approach led to effective passivation of channel defects such as negative-U defects, and ionized-oxygen-vacancy defects. With bilayer ITO-IGZO, we demonstrated 10x negative/positive bias stress (NBS/PBS), and 4x negative bias illumination stress (NBIS) improvement against the conventional mono-IGZO devices. Furthermore, under a low-thermal budget constraint, we implemented a sacrificial replacement gate stress memorization technique to enhance the ferroelectric phase to enable a double-gated (DG) IGZO FeFET. Our reliability-optimized DG ITO-IGZO FeFETs exhibit an enhanced memory window (MW) of 1.7V, excellent memory-write endurance of 10 7 cycles, outstanding memory retention with high I ON /I OFF of 10 6 after 10 4 s, record-low NBS/PNS V TH shift of 30mV, and NBIS V TH shift of 110mV after stress time of 1000s. These devices set a new oxide thin-film transistor (TFT) reliability record making major strides toward highly reliable BEOL logic and memory switches.

Researcher/Author:

Chun-Kuei Chen, Zefeng Xu, Sonu Hooda, Jieming Pan, Evgeny Zamburg, and Aaron Voon-Yew Thean

Published in:

2023 International Electron Devices Meeting (IEDM)

Date Added to IEEE Xplore: 07 February 2024

To download the paper, please proceed to:

- Home

- Negative-U Defect Passivation in Oxide-Semiconductor by Channel Defect Self-Compensation Effect to achieve Low Bias Stress VTH Instability of Low-Thermal Budget IGZO TFT and FeFETs

Singapore Hybrid-Integrated Next-Generation μ-Electronics (SHINE) Centre

- Block E6, #E6-5-3, 5 Engineering Drive 1, Singapore 117608

- +65 6601 8522

- shine@nus.edu.sg