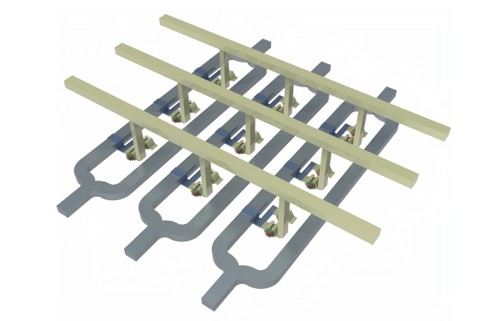

Compute-in-memory (CIM) architectures offer a promising approach to improving data-movement efficiency in data-intensive computing workloads, particularly for deep neural networks. However, the scalability of conventional CIM arrays is fundamentally constrained by bitline (BL) IR losses and the associated error accumulation arising from increased wire resistance as array dimensions scale. In this work, we propose a two-transistor–one-modulator (2T1M) electro-optic memory array featuring an optical BL that effectively eliminates BL IR loss and capacitive loading limitations. In each memory cell, dot-product operations are performed using ferroelectric FET (FeFET) devices operating in the subthreshold regime, with the resulting currents accumulated via phase modulation of an optical carrier. An ultra-low-loss, compact lithium-niobate-on-insulator (LNOI) photonic modulator is employed to enable energy-efficient electro-optic conversion. Photonic waveguide BL readout is implemented using pairs of shared Mach–Zehnder interferometers (MZIs) to maximize column-level layout efficiency. By removing BL IR loss, the proposed architecture enables array sizes of up to 3750 kb and achieves up to a 45% improvement in inference accuracy on a large-scale ALBERT transformer model compared with conventional CIM arrays.

Researcher/Author:

Zhao Shi, Yang Jie, Xu Zefeng

Conference Name : Symposium on VLSI Technology & Circuits 2025

Location : Kyoto, Japan

Date : 8-12 June 2025