- Asian Deans’ Forum Visit to SHINE Centre

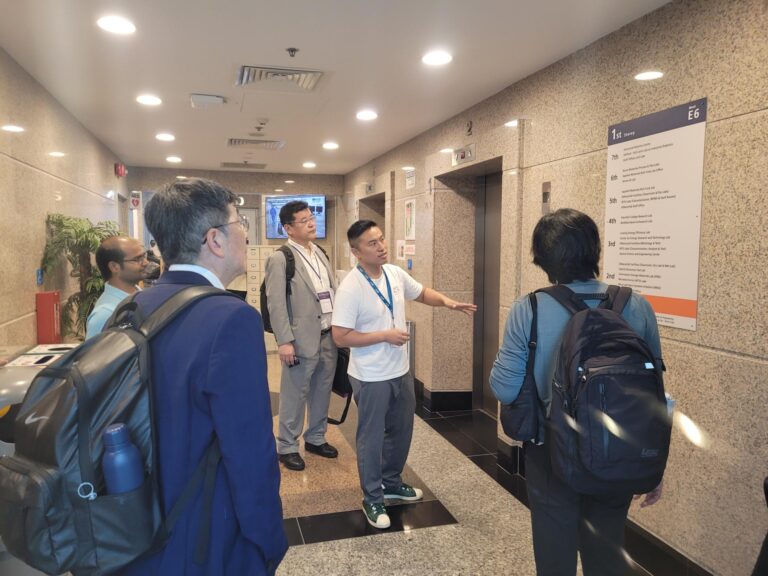

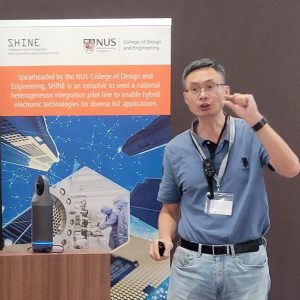

SHINE proudly hosted participants from the Asian Deans’ Forum 2024 on 18 November, offering them an exclusive look into our advanced nanofabrication and microelectronics facilities.

The Asian Deans’ Forum 2024 – The Rising Stars Women in Engineering Workshop, organized by Asia’s top engineering institutions and hosted by the National University of Singapore, aims to unite young women professionals in engineering from around the globe. This workshop fosters collaboration among scholars, researchers, and engineers pursuing academic careers, while serving as a platform for scientific and career-focused discussions that empower women academic leaders in Asia.

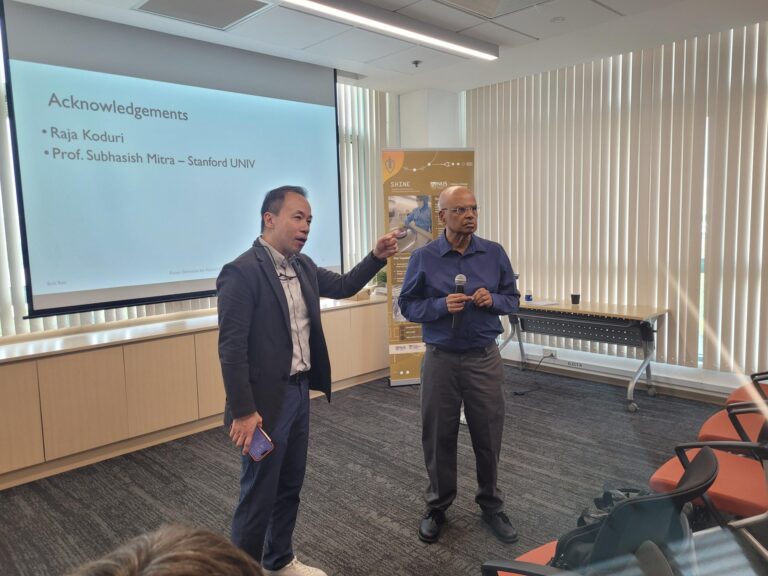

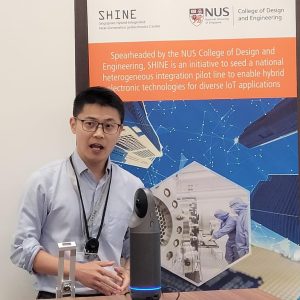

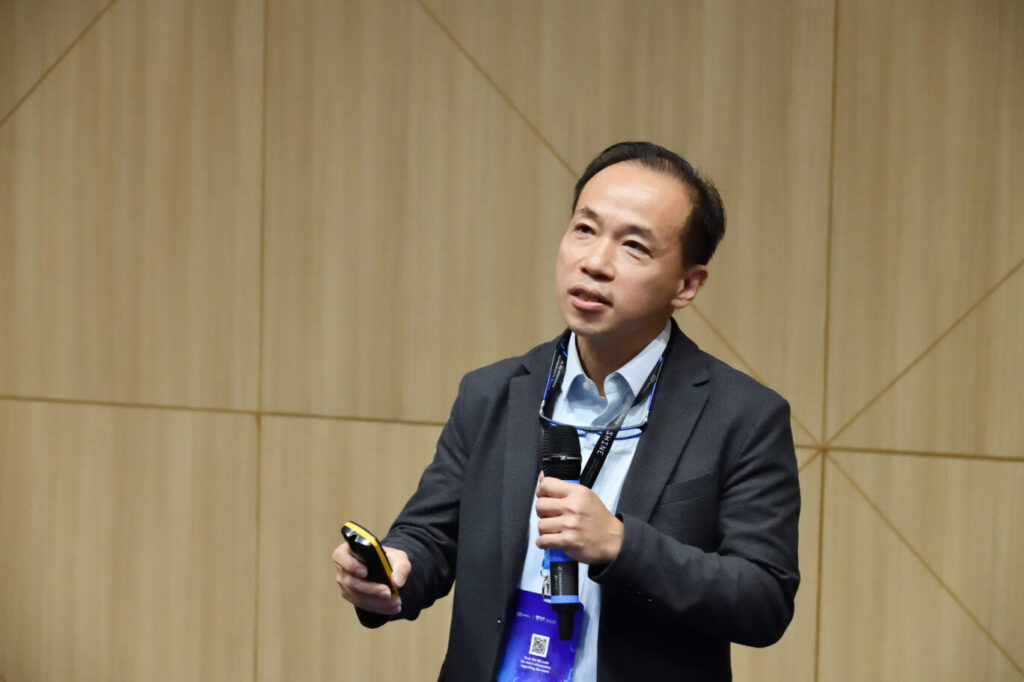

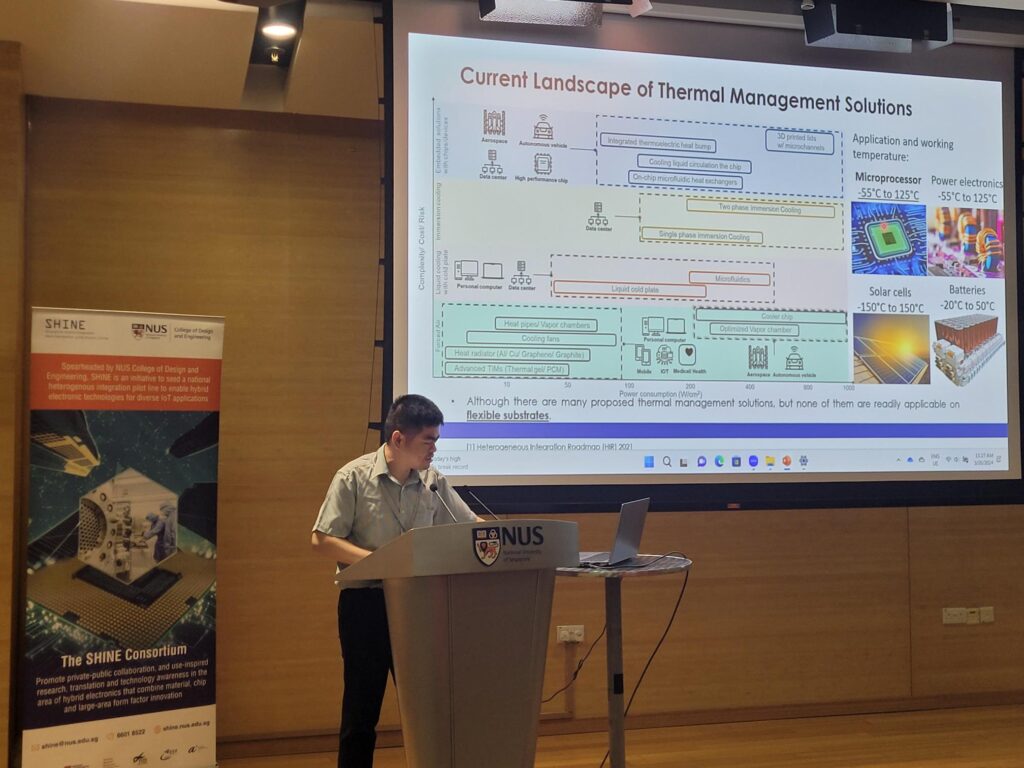

Dr. David Xu, Process Engineering Research Lead, kicked off the visit with an engaging overview of SHINE and E6NanoFab’s capabilities. Participants explored our cleanrooms of varying classifications and dry labs, gaining insights into cutting-edge technologies in deposition, lithography, metrology, characterization, and packaging.

We extend our deepest gratitude to the dedicated team of researchers, engineers, and laboratory officers at the Packaging Facilities @ SHINE Centre and E6NanoFab for their exceptional efforts in making the tour a resounding success.