Publication

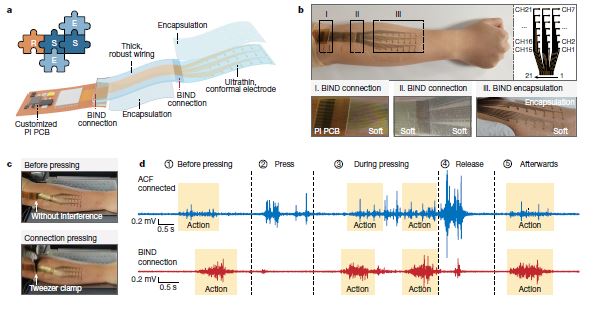

Stretchable hybrid devices have enabled high-fidelity implantable and on-skin monitoring of physiological signals. These devices typically contain soft modules that match the mechanical requirements in humans and soft robots, rigid modules containing Si-based microelectronics and protective encapsulation modules. To make such a system mechanically compliant, the interconnects between the modules need to tolerate stress concentration that may limit their stretching and ultimately cause debonding failure. Here, we report a universal interface that can reliably connect soft, rigid and encapsulation modules together to form robust and highly stretchable devices in a plug-and-play manner. The interface, consisting of interpenetrating polymer and metal nanostructures, connects modules by simply pressing without using pastes. Its formation is depicted by a biphasic network growth model. Soft–soft modules joined by this interface achieved 600% and 180% mechanical and electrical stretchability, respectively. Soft and rigid modules can also be electrically connected using the above interface. Encapsulation on soft modules with this interface is strongly adhesive with an interfacial toughness of 0.24 N mm−1. As a proof of concept, we use this interface to assemble stretchable devices for in vivo neuromodulation and on-skin electromyography, with high signal quality and mechanical resistance. We expect such a plug-and-play interface to simplify and accelerate the development of on-skin and implantable stretchable devices.

Researcher/Author: Ying Jiang (NTU), Shaobo Ji (NUS), Jing Sun (SIAT/CAS), Jianping Huang (SIAT/CAS), Yuanheng Li, Guijin Zou (A*STAR IHPC), Teddy Salim (NTU), Changxian Wang (NTU), Wenlong Li (A*STAR IME), Haoran Jin (NTU/NUS), Jie Xu (Standford), Sihong Wang (Stanford), Ting Lei (Standford), Xuzhou Yan (Stanford), Wendy Yen Xian Peh (NUS), Shih-Cheng Yen (NUS), Zhihua Liu (NUS), Mei Yu (SIAT/CAS), Hang Zhao (SIAT/CAS), Zechao Lu (SIAT/CAS), Guanglin Li (SIAT/CAS), Huajian Gao (A*STAR IHPC), Zhiyuan Liu (SIAT/CAS), Zhenan Bao (Standford) & Xiaodong Chen (NTU)

Nature volume 614, pages456–462 (2023)

https://www.nature.com/articles/s41586-022-05579-z